### HS100 MuxCapacitor<sup>®</sup> Plus Forward Converter Chip Set

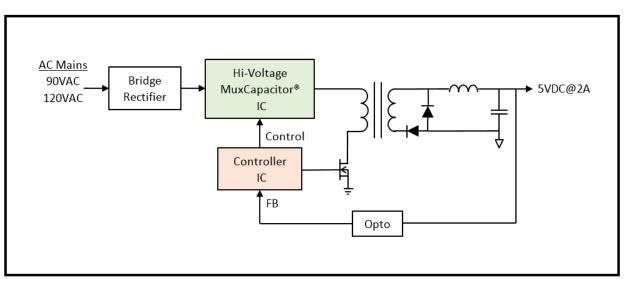

The Helix Semiconductors HS100 Mux-Capacitor Plus Forward Converter two-chip set solution offers the highest energy efficiency for a 110VAC/10W or 220VAC/5W AC-DC isolated power supply. A multi-gain MuxCapacitor delivers the optimum voltage to a forward converter. The forward converter employs an advanced pulse skipping algorithm to maximize no-load and standby operation power efficiency.

The HS100 two chip set includes reset, internal references and regulation & gain control logic. The chip set's high efficiency reduces thermal loading for lower packaging costs. Other output voltages are available with a simple gain trim.

### Features

- 85-264VAC Input Voltage

- High Voltage MuxCapacitor

- Soft-Start

- 5V, 2A Output Voltage @ 120VAC

- 5V, 1A Output Voltage @ 240VAC

- ±5% Output Voltage Regulation

- > 95% Efficiency @ 2A

- > 92% Efficiency @ 200mA

- 10mW No-Load Power Consumption

## **Applications**

- Smart Outlets

- IoT and IIoT Gateways

- Remote Sensors

- Smoke and CO Detectors

## HS100 Block Diagram

#### Table of Contents

| 1      |    | Pin C                                                                                       | Configuration and Description5                                                                                                                                                                                                                                        |

|--------|----|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2      |    | Abso                                                                                        | lute Maximum Ratings9                                                                                                                                                                                                                                                 |

| 3      |    | Reco                                                                                        | mmended Operating Conditions10                                                                                                                                                                                                                                        |

| 4      |    | Parar                                                                                       | metric Specifications11                                                                                                                                                                                                                                               |

| 5      |    | Funct                                                                                       | tional Description                                                                                                                                                                                                                                                    |

|        | 5. | 1                                                                                           | HS100 MuxCapacitor IC20                                                                                                                                                                                                                                               |

|        |    | 5.1.1                                                                                       | MuxCapacitor Voltage Divider21                                                                                                                                                                                                                                        |

|        |    | 5.1.2                                                                                       | Dickson Charge Pumps21                                                                                                                                                                                                                                                |

|        |    | 5.1.3                                                                                       | Level Shifters21                                                                                                                                                                                                                                                      |

|        |    | 5.1.4                                                                                       | Soft-Start Current Limiter21                                                                                                                                                                                                                                          |

|        |    | 5.1.5                                                                                       | 3.2MHz Oscillator22                                                                                                                                                                                                                                                   |

|        | 5. | 2                                                                                           | HS100 Control IC23                                                                                                                                                                                                                                                    |

|        |    | 5.2.1                                                                                       | Line-Side Bandgap Voltage and Current Reference Generator                                                                                                                                                                                                             |

|        |    | 5.2.1                                                                                       | Ene-Side Bandgap Voltage and Current Reference Generator                                                                                                                                                                                                              |

|        |    | 5.2.1                                                                                       |                                                                                                                                                                                                                                                                       |

|        |    |                                                                                             | 5.0V Linear Voltage Regulator24                                                                                                                                                                                                                                       |

|        |    | 5.2.2                                                                                       | 5.0V Linear Voltage Regulator                                                                                                                                                                                                                                         |

|        |    | 5.2.2<br>5.2.3                                                                              | 5.0V Linear Voltage Regulator                                                                                                                                                                                                                                         |

|        |    | 5.2.2<br>5.2.3<br>5.2.4                                                                     | 5.0V Linear Voltage Regulator                                                                                                                                                                                                                                         |

|        |    | 5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                                                            | 5.0V Linear Voltage Regulator                                                                                                                                                                                                                                         |

|        |    | 5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6                                                   | 5.0V Linear Voltage Regulator       24         Power-on-Reset       24         VTOI and Current Manifold       25         Oscillator       25         10V Linear Voltage Regulator       25         Forward PID Controller       25                                   |

|        |    | 5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.6                                          | 5.0V Linear Voltage Regulator       24         Power-on-Reset       24         VTOI and Current Manifold       25         Oscillator       25         10V Linear Voltage Regulator       25         Forward PID Controller       25         Country Selector       26 |

|        | 5. | 5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9                        | 5.0V Linear Voltage Regulator       24         Power-on-Reset       24         VTOI and Current Manifold       25         Oscillator       25         10V Linear Voltage Regulator       25         Forward PID Controller       25         Country Selector       26 |

| 6      | 5. | 5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9<br>3                   | 5.0V Linear Voltage Regulator24Power-on-Reset24VTOI and Current Manifold25Oscillator2510V Linear Voltage Regulator25Forward PID Controller25Country Selector26Over-Current Protection26                                                                               |

| 6<br>7 | 5. | 5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9<br>3<br>Refer          | 5.0V Linear Voltage Regulator                                                                                                                                                                                                                                         |

|        | 5. | 5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9<br>3<br>Refer<br>Packa | 5.0V Linear Voltage Regulator                                                                                                                                                                                                                                         |

#### Table of Tables

| 1  | HS100 MuxCapacitor IC Pin Assignments                 |

|----|-------------------------------------------------------|

| 2  | HS100 Control IC Pin Assignments7                     |

| 3  | Absolute Maximum Ratings9                             |

| 4  | Recommended Operating Conditions10                    |

| 5  | Line-Side Bandgap Voltage Reference11                 |

| 6  | 5.0V Linear Voltage Regulator                         |

| 7  | Power-On-Reset                                        |

| 8  | Hysteresis Comparators (Country Selector)13           |

| 9  | MuxCapacitor Voltage Divider (MuxCapacitor IC Only)14 |

| 10 | Low-Frequency RC Oscillator                           |

| 11 | 3.2MHz Oscillator (MuxCapacitor IC Only)15            |

| 12 | Sawtooth Generator15                                  |

| 13 | Forward PID Control Loop16                            |

| 14 | CMOS Digital Inputs                                   |

| 15 | CMOS Digital Outputs                                  |

| 16 | MuxCapacitor Gain Selection Truth Table21             |

| 17 | Oscillator Frequency Control                          |

| 18 | Soft-Start Timer Program Settings                     |

| 19 | Test Select Truth Table                               |

| 20 | NAND-Tree Test Sequence                               |

| 21 | HS100 System Characteristics                          |

| 22 | Revision History                                      |

### Table of Figures

| 1 | Pin Configuration                     | 5    |

|---|---------------------------------------|------|

|   | HS100 MuxCapacitor IC Block Diagram   |      |

| 3 | HS100 Control IC Block Diagram        | . 19 |

| 4 | POR Threshold Voltages                | .24  |

| 5 | Digital Control Block Diagram         | . 27 |

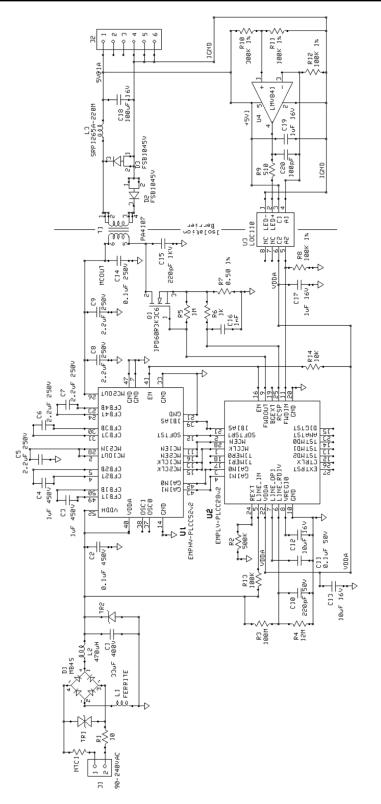

| 6 | HS100 Japan/US Application Schematic  | .31  |

| 7 | HS100 Universal Application Schematic | .32  |

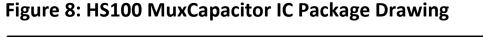

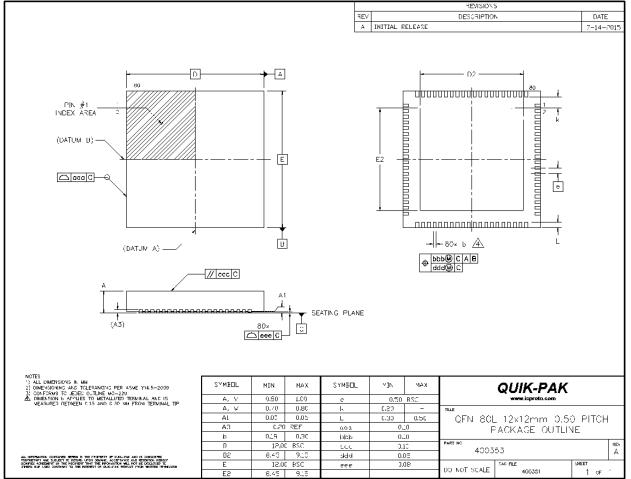

| 8 | HS100 MuxCapacitor IC Package Drawing | .33  |

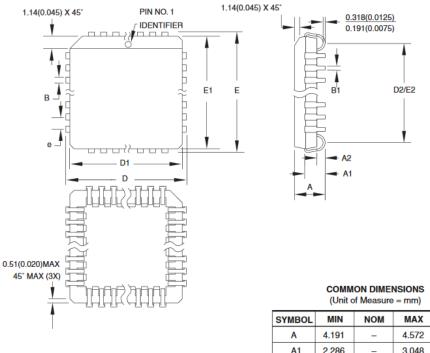

| 9 | HS100 Control IC Package Drawing      | .34  |

## **1** Pin Configuration and Description

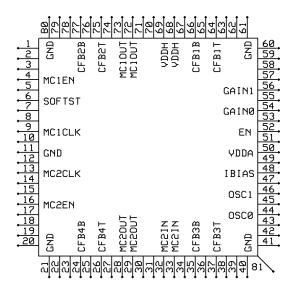

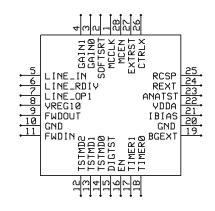

### Figure 1: Pin Configuration

HS100 Control IC – PLCC28

HS100 MuxCapacitor IC – QFN80

The HS100 chip set is provided in prototype packaging for test development purposes ONLY. Special handling precautions are required due to the presence of high voltage.

### Table 1: HS100 MuxCapacitor IC Pin Assignments

| Pin No. | Name   | Description                      |

|---------|--------|----------------------------------|

| 4       | MC1EN  | MuxCapacitor 1 Enable: Input Pin |

|         |        | 0 = Disable, 1 = Enable          |

|         |        | Internal Pull-Down               |

| 6       | SOFTST | Soft-Start Timer: Input Pin      |

|         |        | 0 = Disable, 1 = Enable          |

|         |        | Internal Pull-Down               |

| 9       | MC1CLK  | MuxCapa                                  | citor 1 Clo                                            | ck: Input Pin     |          |  |  |  |  |

|---------|---------|------------------------------------------|--------------------------------------------------------|-------------------|----------|--|--|--|--|

| 11      | GND     | -                                        | ge Ground                                              |                   |          |  |  |  |  |

| 13      | MC2CLK  | MuxCapa                                  | citor 2 Clo                                            | ck: Input pin     |          |  |  |  |  |

| 16      | MC2EN   | MuxCapa                                  | citor 2 Ena                                            | ble: Input Pin    |          |  |  |  |  |

|         |         | 0 = Disabl                               | e, 1 = Enal                                            | ole               |          |  |  |  |  |

|         |         | Internal P                               | ull-Down                                               |                   |          |  |  |  |  |

| 21, 40, | GND     | High Volta                               | igh Voltage Ground                                     |                   |          |  |  |  |  |

| 61, 80  |         |                                          |                                                        |                   |          |  |  |  |  |

| 24      | СГВ4В   | External F                               | xternal Flying Capacitor 4 (-)                         |                   |          |  |  |  |  |

| 26      | CFB4T   | External F                               | xternal Flying Capacitor 4 (+)                         |                   |          |  |  |  |  |

| 28, 29  | MC2OUT  | MuxCapa                                  | AuxCapacitor 2: Analog Output Pin                      |                   |          |  |  |  |  |

| 32, 33  | MC2IN   | External N                               | xternal MuxCapacitor 2: Analog Input Pin               |                   |          |  |  |  |  |

| 35      | CFB3B   | External F                               | External Flying Capacitor 3 (-)                        |                   |          |  |  |  |  |

| 37      | CFB3T 🥂 |                                          | External Flying Capacitor 3 (+)                        |                   |          |  |  |  |  |

| 44      | OSCO    | Oscillator Frequency Control: Input Pins |                                                        |                   |          |  |  |  |  |

| 46      | OSC1    | OSC1                                     | OSC1 OSC0 Freq Out - MHz                               |                   |          |  |  |  |  |

|         |         | 0                                        | 0 0 1.6 MHz                                            |                   |          |  |  |  |  |

|         |         | 0                                        | 1                                                      | 0.8 MHZ           |          |  |  |  |  |

|         |         | 1                                        | 0                                                      | 0.4 MHz           |          |  |  |  |  |

|         |         | 1                                        | 1                                                      | Disabled          |          |  |  |  |  |

|         |         |                                          | ull-Downs                                              |                   |          |  |  |  |  |

| 48      | IBIAS   | -                                        |                                                        | ference: Analog   | -        |  |  |  |  |

| 50      | VDDA    |                                          |                                                        | Analog Input Pi   | n        |  |  |  |  |

| 52      | EN      |                                          | able: Inpu                                             |                   |          |  |  |  |  |

|         |         |                                          | e, 1 = Enal                                            | ble               |          |  |  |  |  |

|         |         | Internal P                               |                                                        |                   |          |  |  |  |  |

| 54      | GAINO   |                                          |                                                        | Control: Input Pi |          |  |  |  |  |

| 56      | GAIN1   | GAIN1                                    | GAIN0                                                  | MX1 Gain          | MX0 Gain |  |  |  |  |

|         |         | 0                                        | 0                                                      | 1                 | 1        |  |  |  |  |

|         |         | 0                                        | 1                                                      | 2/3               | 2/3      |  |  |  |  |

|         |         | 1                                        | 0                                                      | 1/2               | 1/2      |  |  |  |  |

|         |         |                                          |                                                        |                   |          |  |  |  |  |

|         |         |                                          | Internal Pull-Downs<br>External Flying Capacitor 1 (+) |                   |          |  |  |  |  |

| 64      | CFB1T   |                                          |                                                        |                   |          |  |  |  |  |

| 66      | CFB1B   |                                          | · • ·                                                  | acitor 1 (-)      |          |  |  |  |  |

| 68, 69  |         |                                          |                                                        | alog Input Pin    |          |  |  |  |  |

| 72.73   | MC1OUT  |                                          |                                                        | alog Output Pin   |          |  |  |  |  |

| 75      | CFB2T   | External F                               | iying Capa                                             | citor 2 (+)       |          |  |  |  |  |

| 77          | CFB2B           | External Flying Capacitor 2 (-) |

|-------------|-----------------|---------------------------------|

| 81          | TPAD            | Thermal Pad: No Connection      |

| 1,2,3,5, 7, | 8,10,12,14,15,  | Unused, Do Not Connect          |

| 17,14,15,1  | 17,18,19,20,22, |                                 |

| 23,25,27,3  | 80,31,34,36,38, |                                 |

| 39,41,42,4  | 13,45,47,49,51, |                                 |

| 53,55,57,5  | 58,59,60,62,63, |                                 |

| 65,67,70,7  | 71,74,76,78.79  |                                 |

### Table 2: HS100 Control IC Pin Assignments

| Pin No. | Name      | Description           |                                                       |              |                           |  |  |  |  |  |

|---------|-----------|-----------------------|-------------------------------------------------------|--------------|---------------------------|--|--|--|--|--|

| 1       | MCCLK     | MuxCapacit            | or Clock: Ou                                          | tput Pin     |                           |  |  |  |  |  |

| 2       | SOFSTRT   | Soft Start Ti         | mer: Output                                           | : Pin        |                           |  |  |  |  |  |

| 3       | GAIN0     | MuxCapacit            | MuxCapacitor Gain Control: Output Pins                |              |                           |  |  |  |  |  |

| 4       | GAIN1     |                       |                                                       |              |                           |  |  |  |  |  |

| 5       | LINE_IN 🛕 | Rectified Lir         | Rectified Line Voltage: High Voltage Analog Input Pin |              |                           |  |  |  |  |  |

| 6       | LINE_RDIV | Line Voltage          | e Resistor Div                                        | vider: Analo | g Input Pin               |  |  |  |  |  |

| 7       | LINE_OP1  | Source Follo          | Source Follower pin from LINE_RDIV                    |              |                           |  |  |  |  |  |

|         |           | Add externa           | al 0.1µF, 50V                                         | capacitor    |                           |  |  |  |  |  |

| 8       | VERG10    | +10V Regula           | ator: Analog                                          | Output Pin   |                           |  |  |  |  |  |

|         |           | Add externa           | al 10µF, 16V                                          | capacitor    |                           |  |  |  |  |  |

| 9       | FWDOUT    | Forward Co            | nverter FET                                           | Driver: Outp | out Pin                   |  |  |  |  |  |

| 10      | GND       | Low Voltage           | e Ground                                              |              |                           |  |  |  |  |  |

| 11      | FWDIN     | Forward Co            | nverter Opto                                          | Feedback:    | Analog Input Pin          |  |  |  |  |  |

| 12      | TSTMD2    | Test Mode             | Control: Inpu                                         | ıt Pins      |                           |  |  |  |  |  |

| 13      | TSTMD1    | TSTMD2                | TSTMD1                                                | TSTMD0       | Test Mode Operation       |  |  |  |  |  |

| 14      | TSTMD0    | 0                     | 0                                                     | 0            | DIGTST: OC Detect         |  |  |  |  |  |

|         |           | 0                     | 0                                                     | 1            | DIGTST: FWD Clamp         |  |  |  |  |  |

|         |           | 0                     | 1                                                     | 0            | DIGTST: FWD Softstart OK  |  |  |  |  |  |

|         |           | 0                     | 1                                                     | 1            | DIGTST: 100kHz Ocsillator |  |  |  |  |  |

|         |           | 1                     | 0                                                     | 0            | Reset OC Detect           |  |  |  |  |  |

|         |           | 1                     | 0                                                     | 1            | Disable FWD PID           |  |  |  |  |  |

|         |           | 1                     | 1                                                     | 0            | ANATST: Bandgap Voltage   |  |  |  |  |  |

|         |           | 1 1 1 Logic Test Mode |                                                       |              |                           |  |  |  |  |  |

|         |           | Internal Pul          | Internal Pull-Downs                                   |              |                           |  |  |  |  |  |

| 15      | DIGTST    | Digital Test          | Mux: Outpu                                            | t Pin        |                           |  |  |  |  |  |

| 16      | EN        | Device Enab           | ole: Input Pir                                        |              |                           |  |  |  |  |  |

|    |        |            |                                      | -                     |             |  |  |  |

|----|--------|------------|--------------------------------------|-----------------------|-------------|--|--|--|

|    |        |            | 0 = Disable, 1 = Enable              |                       |             |  |  |  |

|    |        | Internal P | Internal Pull-Down                   |                       |             |  |  |  |

| 17 | TIMER1 | Soft Start | Soft Start Timer Control: Input Pins |                       |             |  |  |  |

| 18 | TIMERO | TIMER1     | <b>TIMER0</b>                        | Soft Start Delay      |             |  |  |  |

|    |        | 0          | 0                                    | 10 msec               |             |  |  |  |

|    |        | 0          | 1                                    | 30 msec               |             |  |  |  |

|    |        | 1          | 0                                    | 20 msec               |             |  |  |  |

|    |        | 1          | 1                                    | 40 msec               |             |  |  |  |

|    |        | Internal P | ull-Downs                            |                       |             |  |  |  |

| 19 | BGEXT  | Optional E | External 1.                          | 25V Bandgap: Analog   | Input Pin   |  |  |  |

|    |        | Set CTRLX  | = 1 for us                           | e with external bandg | jap.        |  |  |  |

| 20 | GND    | Low Volta  | ge Ground                            |                       |             |  |  |  |

| 21 | IBIAS  | Bias Curre | ent Referer                          | nce: Analog Output Pi | n           |  |  |  |

| 22 | VDDA   | +5V Regul  | ator: Anal                           | og Output Pin         |             |  |  |  |

|    |        | Add exter  | nal 10µF, 1                          | L6V capacitor         |             |  |  |  |

| 23 | ANATST | Analog Te  | st Mux: Ou                           | utput Pin             |             |  |  |  |

| 24 | REXT   | External B | ias Resisto                          | or: Analog Input Pin  |             |  |  |  |

|    |        | Add exter  | nal 499K 1                           | % resistor from REXT  | pin to GND  |  |  |  |

| 25 | RCSP   | Forward C  | Converter (                          | Current Sense: Analog | g Input Pin |  |  |  |

|    |        | Add exter  | nal 0.5Ω 1                           | % current sense resis | tor to GND. |  |  |  |

| 26 | CTRLX  | Control/T  | est Mode:                            | Input Pin             |             |  |  |  |

|    |        | 0 = Disabl | e, 1 = Enat                          | le Control Mode and   | Test Modes  |  |  |  |

|    |        | Internal P | Internal Pull-Down                   |                       |             |  |  |  |

| 27 | EXTRST | External R | eset: Inpu                           | t Pin                 |             |  |  |  |

|    |        | 0 = Disabl | 0 = Disable, 1 = Enable              |                       |             |  |  |  |

|    |        | Internal P | ull-Down                             |                       |             |  |  |  |

| 28 | MCEN   | MuxCapa    | citor Enabl                          | e: Output Pin         |             |  |  |  |

### 2 Absolute Maximum Ratings

The HS100 chip-set can be exposed to the following extremes without permanent damage to device operation. Performance is not guaranteed at these extremes.

#### **Table 3: Absolute Maximum Ratings**

| Symbol             | Parameter                                 | Min  | Тур | Мах | Unit | Condition                       |

|--------------------|-------------------------------------------|------|-----|-----|------|---------------------------------|

| V <sub>HVIO</sub>  | Voltage at all High-Voltage<br>Analog I/O | -0.3 |     | 350 | V    | At pins VDDH, MC2IN,<br>LINE_IN |

| V <sub>MVIO</sub>  | Voltage at all Mid-Voltage<br>Analog I/O  | -0.3 |     | 40  | V    | At pins LINE_RDIV,<br>LINE_0P1  |

| V <sub>LVIO</sub>  | Voltage at all Low-Voltage<br>I/O         | -0.3 |     | 6.0 | V    |                                 |

| V <sub>HBM</sub>   | HBM ESD Voltage                           |      |     | 2   | ΚV   | Human Body Model                |

| V <sub>CDM</sub>   | CDM ESD Voltage                           |      |     | 500 | V    | Charge Device Model             |

| V <sub>MM</sub>    | MM ESD Voltage                            |      |     | 200 | V    | Machine Model                   |

| V <sub>LU</sub>    | Latchup Test Limits                       | -100 |     | 100 | mA   |                                 |

| T <sub>store</sub> | Storage Temperature<br>Range              | -40  |     | 125 | °C   |                                 |

| Тј                 | Junction Temperature<br>Range             | -40  |     | 125 | °C   |                                 |

### **3** Recommended Operating Conditions

The HS100 chip-set is designed to operate within the design limits specified in the Parametric Specifications when the conditions of the following table are not exceeded.

#### **Table 4: Recommended Operating Conditions**

| Symbol            | Parameter                                  | Min  | Тур  | Max  | Unit | Condition                       |

|-------------------|--------------------------------------------|------|------|------|------|---------------------------------|

| V <sub>HVIO</sub> | Voltage at all High-<br>Voltage Analog I/O | 127  | 170  | 340  | V    | At pins VDDH, MC2IN,<br>LINE_IN |

| V <sub>MVIO</sub> | Voltage at all Mid-Voltage<br>Analog I/O   | 12.7 | 17.0 | 34.0 | V    | At pins LINE_RDIV,<br>LINE_0P1  |

| $V_{\text{LVIO}}$ | Voltage at all Low-Voltage<br>Analog I/O   | 4.5  | 5.0  | 5.5  | V    |                                 |

| T <sub>a</sub>    | Ambient Temperature<br>Range               | -40  |      | 85   | °C   |                                 |

| Tj                | Junction Temperature<br>Range              | -40  |      | 125  | °C   |                                 |

### 4 Parametric Specifications

The electrical characteristics of the HS100 Chip-Set are tested according to the following criteria noted in the Test column of each table:

- T : Directly or indirectly tested at 100% for production or prototype samples

- Q : Tested for qualification and bench evaluation

- D : Guaranteed by Design

All specifications apply only to the HS100 Control IC unless otherwise noted.

#### Table 5: Line-Side Bandgap Voltage Reference

| Symbol            | Parameter                   | Conditions                                      | Test | Min <sup>1</sup> | Typ <sup>2</sup> | Max <sup>1</sup> | Unit             |

|-------------------|-----------------------------|-------------------------------------------------|------|------------------|------------------|------------------|------------------|

| VLINE0P1          | Supply Voltage              | At LINE_0P1                                     | D    | 12.7             |                  | 34.0             | V                |

| ILINEDP1          | Supply Current              | At LINE_0P1; en=1                               | D    |                  | 8.3              |                  | μA               |

| V <sub>BG</sub>   | Output Voltage              | At ANATST; No trim                              | Т    | 1.158            | 1.219            | 1.28             | V                |

| V <sub>tol</sub>  | Output Voltage<br>Tolerance | At ANATST; No trim                              | т    |                  |                  | ±5               | %                |

| Тс                | Temp. coefficient           | At ANATST                                       | Q    |                  |                  | 300              | ppm/°C           |

| PSR               | Power Supply<br>Rejection   | At ANATST; f=10KHz<br>& 100KHz                  | Q    | 70               |                  |                  | dB <sub>20</sub> |

| PSR <sub>DC</sub> | DC supply rejection         | At DC; f=0.001Hz                                | Q    | 90               |                  |                  | dB <sub>20</sub> |

| V <sub>N</sub>    | Output Noise                | Integrated Noise; 10Hz<br>≤ f ≤ 10KHz           | D    |                  |                  | 1000             | µVrms            |

| I <sub>BIAS</sub> | Output Current              | At IBIAS; T=25°C;<br>R <sub>EXT</sub> =500KΩ 1% | D    | 0.94             | 1.0              | 1.06             | μA               |

| CL                | Output Load<br>Capacitance  | At VBG                                          | D    |                  |                  | 2                | pF               |

| t <sub>RAMP</sub> | Supply Ramp Time            | At LINE_0P1                                     | D    | 0.1              |                  | 100              | mS               |

| ts                | Startup time                | At VBG; For 100µS<br>ramp at LINE_0P1           | D    |                  |                  | 2000             | μS               |

| I <sub>LKG</sub>  | Disabled Leakage<br>Current | en=0                                            | D    |                  |                  | 10               | nA               |

Notes: 1. Min and Max values are valid over Operating Conditions, unless otherwise stated.

2. Typ values are valid at typical Operating Conditions and typical process Parameters.

### Table 6: 5.0V Linear Voltage Regulator

| Symbol           | Parameter                    | Condition                                                       | Test | Min <sup>1</sup> | Typ <sup>2</sup> | Max <sup>1</sup> | Unit |  |

|------------------|------------------------------|-----------------------------------------------------------------|------|------------------|------------------|------------------|------|--|

| $V_{REF}$        | Reference Input<br>Voltage   | Bandgap voltage at<br>V <sub>BG</sub>                           | D    |                  | 1.219            |                  | V    |  |

| V <sub>out</sub> | Output Voltage               | At VDDA; 100μA ≤<br>I <sub>LOAD</sub> ≤ 10mA                    | т    | 4.5              | 5.0              | 5.5              | V    |  |

| VR               | Line Regulation              | At VDDA; I <sub>LOAD</sub> = 2mA;                               | Т    |                  |                  | 100              | m%   |  |

| LR               | Load Regulation              | At VDDA; 0 ≤ I <sub>LOAD</sub> ≤ 10mA                           | т    |                  |                  | 100              | m%   |  |

| A <sub>OL</sub>  | Open Loop Gain               | In-Circuit; I <sub>LOAD</sub> = 2mA<br>C <sub>LOAD</sub> =11μF, | D    | 90               |                  |                  | dB   |  |

|                  |                              | I <sub>LOAD</sub> = 1μA                                         | D    | 80               |                  |                  |      |  |

| фм               | Phase Margin                 | In-Circuit; I <sub>LOAD</sub> = 2mA<br>C <sub>LOAD</sub> =11μF  | D    | 70               |                  |                  | Deg. |  |

| ,                |                              | I <sub>LOAD</sub> = 1μA                                         | D    | 65               |                  |                  |      |  |

| PSRR             | Power Supply                 | f=10KHz; C <sub>L</sub> =11μF;<br>Ι <sub>LOAD</sub> = 2mA       | Q    | 40               |                  |                  | dB   |  |

| PORK             | Rejection Ratio              | f=dc; C <sub>L</sub> =11µF; I <sub>LOAD</sub> =<br>2mA          | Q    | 60               |                  |                  | dB   |  |

| V <sub>os</sub>  | Input-Referred Offset        | 6σ Mismatch; I <sub>LOAD</sub> =<br>2mA                         | D    |                  |                  | 15               | m∨   |  |

| I <sub>SUP</sub> | Power Supply Current         | en=1; No Load;                                                  | D    |                  |                  | 1                | μΑ   |  |

| I <sub>lkg</sub> | Off-State Leakage<br>Current | en=0; No Load                                                   | D    |                  |                  | 10               | nA   |  |

Notes: 1. Min and Max values are valid over Operating Conditions, unless otherwise stated.

2. Typ values are valid at typical Operating Conditions and typical process Parameters.

#### **Table 7: Power-On-Reset**

| Symbol           | Parameter                | Condition            | Test | Min <sup>1</sup> | Тур² | Max <sup>1</sup> | Unit |

|------------------|--------------------------|----------------------|------|------------------|------|------------------|------|

| V <sub>SUP</sub> | Supply Voltage           | At VDDA              | D    | 4.5              | 5.0  | 5.5              | V    |

| V <sub>POR</sub> | POR Threshold            |                      | Q    | 2.8              | 3.0  | 3.2              | V    |

| V <sub>HYS</sub> | Input Voltage Hysteresis |                      | Q    | 200              | 300  | 450              | mV   |

| I <sub>SUP</sub> | Enabled Drain Current    | For information only | D    |                  | 3.1  |                  | μA   |

Notes: 1. Min and Max values are valid over Operating Conditions, unless otherwise stated.

2. Typ values are valid at typical Operating Conditions and typical process Parameters.

#### Table 8: Hysteresis Comparators (Country Selector)

| Symbol             | Parameter                               | Condition                                        | Test | Min <sup>1</sup> | Typ <sup>2</sup> | Max <sup>1</sup> | Unit   |

|--------------------|-----------------------------------------|--------------------------------------------------|------|------------------|------------------|------------------|--------|

| V <sub>ICM</sub>   | Input Common-Mode<br>Voltage Range      |                                                  | D    | 0.7              | 1.25             | 2                | v      |

| •                  | Veltere Cein                            | L>H at OUT;<br>V <sub>ICM</sub> =1.25V; Hyst OFF | D    | 1.0              |                  |                  |        |

| Av                 | Voltage Gain                            | H>L at OUT;<br>V <sub>ICM</sub> =0.9V; Hyst OFF  | D    | 1.0              |                  |                  | - KV/V |

|                    |                                         | hyst<1:0>=0                                      | Q    |                  | 0                |                  | mV     |

|                    | lana di Ukasha na sia                   | hyst<1:0>=1                                      | Q    |                  | 10               |                  |        |

| V <sub>HYST</sub>  | <sub>s⊤</sub> Input Hysteresis hy       | hyst<1:0>=2                                      | Q    |                  | 20               |                  |        |

|                    |                                         | hyst<1:0>=3                                      | Q    |                  | 30               |                  |        |

| t <sub>PD_LH</sub> | Comparator Prop.<br>Delay – Low to High | 3mV Overdrive                                    | D    |                  |                  | 20               | μS     |

| t <sub>PD_HL</sub> | Comparator Prop.<br>Delay – High to Low | 3mV Overdrive                                    | D    |                  |                  | 20               | μS     |

| t <sub>RISE</sub>  | Output Rise Time                        | 3mV Overdrive                                    | D    |                  |                  | 10               | nS     |

| t <sub>FALL</sub>  | Output Fall Time                        | 3mV Overdrive                                    | D    |                  |                  | 10               | nS     |

| I <sub>VDDA</sub>  | Power Supply Current                    | en=1; V <sub>DDA</sub> = 5.0V                    | D    |                  | 1.8              |                  | μA     |

| I <sub>LKG</sub>   | Off-State Leakage<br>Current            | en=0; V <sub>DDA</sub> = 5.0∨                    | D    |                  |                  | 10               | nA     |

Notes: 1. Min and Max values are valid over Operating Conditions, unless otherwise stated. 2. Typ values are valid at typical Operating Conditions and typical process Parameters.

### Table 9: MuxCapacitor<sup>®</sup> Voltage Divider (MuxCapacitor IC only)

| Symbol             | Parameter                      | Condition                              | Test | Min <sup>1</sup> | Typ <sup>2</sup> | Max <sup>1</sup> | Unit |

|--------------------|--------------------------------|----------------------------------------|------|------------------|------------------|------------------|------|

| VIN                | Input Voltage                  | At VDDH / MCIN2 pins                   | D    | 90               | 170              | 340              | V    |

| $P_{EFF}$          | Power Efficiency               | At I <sub>MCOUTx</sub> =50mA           | Т    | 95               |                  |                  | %    |

| VOLT               | MuxCapacitor Output<br>Voltage | I <sub>MCOUT</sub> =50mA               | т    | 90               | 1 <b>1</b> 0     | 130              | v    |

| F₅₩                | Switching Frequency            |                                        | D    |                  | 1                |                  | KHz  |

| T <sub>ST</sub>    | SoftStart Timer Period         | Programmable via the<br>Low-Voltage IC | D    |                  | 10               |                  | mS   |

| C <sub>FLYBK</sub> | Flyback Capacitance            |                                        | D    |                  | 3.3              |                  | μF   |

| CHOLD              | Hold Capacitance               |                                        | D    |                  | 7.5              |                  | μF   |

| R <sub>olt</sub>   | Output Resistance              |                                        | D    |                  | 30               |                  | Ω    |

| Імсолт             | Output Load Current<br>Range   | At MCOUTx                              | т    | 0                |                  | 50               | mΑ   |

| Islp               | Enabled Current Drain          | Single stage<br>(static+fcV)           | D    |                  |                  | 120              | μA   |

| l <sub>lkg</sub>   | Disabled Current Drain         |                                        | D    |                  |                  | 0.2              | μA   |

Notes: 1. Min and Max values are valid over Operating Conditions, unless otherwise stated. 2. Typ values are valid at typical Operating Conditions and typical process Parameters.

#### Table 10: Low-Frequency RC Oscillator

| Symbol             | Parameter                    | Condition            | Test | Min <sup>1</sup> | Typ <sup>2</sup> | Max <sup>1</sup> | Unit |

|--------------------|------------------------------|----------------------|------|------------------|------------------|------------------|------|

| fasc               | Oscillator Frequency         | At DIGTST            | Т    | 70               | 100              | 130              | KHz  |

| f <sub>ERR</sub>   | Frequency Accuracy           | No Trim              | Т    | -30              |                  | +30              | %    |

| t <sub>ccJ</sub>   | Cycle-to-Cycle Jitter        |                      | Q    |                  | 25               |                  | nS   |

| t <sub>start</sub> | Startup Time                 |                      | D    |                  | 200              |                  | μS   |

| DC                 | Output Duty Cycle            |                      | Q    | 45               | 50               | 55               | %    |

| I <sub>SUP</sub>   | Drain Current                | For information only | D    |                  |                  | 0.5              | μA   |

| I <sub>LKG</sub>   | Off-State Leakage<br>Current | En=0                 | D    |                  |                  | 10               | nA   |

Notes: 1. Min and Max values are valid over Operating Conditions, unless otherwise stated. 2. Typ values are valid at typical Operating Conditions and typical process Parameters.

### Table 11: 3.2MHz Oscillator (MuxCapacitor IC only)

| Symbol                  | Parameter                      | Condition            | Test | Min <sup>1</sup> | Typ <sup>2</sup> | Max <sup>1</sup> | Unit       |

|-------------------------|--------------------------------|----------------------|------|------------------|------------------|------------------|------------|

| V <sub>SUP</sub>        | Supply Voltage                 | At VDDA              | D    | 4.5              | 5.0              | 5.5              | V          |

| f <sub>osc</sub>        | Oscillator Output OSC<1:0>=0x0 |                      | 1.12 | 1.6              | 2.08             |                  |            |

|                         | Frequency                      | OSC<1:0>=0x1         |      | 0.56             | 0.8              | 1.04             |            |

|                         |                                | OSC<1:0>=0x2         | -  T | 0.28             | 0.4              | 0.52             | — MHz<br>— |

|                         |                                | OSC<1:0>=0x3         |      | -                | -                | -                |            |

| <b>f</b> <sub>ERR</sub> | Frequency Accuracy             | No Trim              | Т    | -30              |                  | 30               | %          |

| DC                      | Output Duty Cycle              |                      | Q    | 45               | 50               | 50               | %          |

| t <sub>start</sub>      | Startup Time                   |                      | D    |                  | 10               |                  | μS         |

| I <sub>SUP</sub>        | Drain Current                  | For information only | D    |                  |                  | 20               | μA         |

| I <sub>LKG</sub>        | Off-State Leakage<br>Current   |                      | D    |                  |                  | 10               | nA         |

Notes: 1. Min and Max values are valid over Operating Conditions, unless otherwise stated. 2. Typ values are valid at typical Operating Conditions and typical process Parameters.

#### Table 12: Sawtooth Generator

| Symbol           | Parameter                    | Condition            | Test | Min <sup>1</sup> | Typ <sup>2</sup> | Max <sup>1</sup> | Unit            |

|------------------|------------------------------|----------------------|------|------------------|------------------|------------------|-----------------|

| V <sub>SUP</sub> | Supply Voltage               | At VDDA              | D    | 4.5              | 5.0              | 5.5              | V               |

| f <sub>CLK</sub> | Clock Frequency              |                      | D    |                  | 100              |                  | KHz             |

| Vicm             | Common-Mode Input<br>Voltage |                      | D    | 0                | 1.25             | 2                | v               |

| V <sub>OUT</sub> | Output Voltage (Pk-Pk)       |                      | D    | 1.9              | 2.7              | 3.5              | V <sub>PP</sub> |

| I <sub>SUP</sub> | Drain Current                | For information only | D    |                  |                  | 20               | μA              |

| I <sub>lkg</sub> | Off-State Leakage<br>Current | En=0                 | D    |                  |                  | 10               | nA              |

Notes: 1. Min and Max values are valid over Operating Conditions, unless otherwise stated.2. Typ values are valid at typical Operating Conditions and typical process Parameters.

### Table 13: Forward PID Control Loop

| Symbol             | Parameter                           | Condition                                            | Test | Min <sup>1</sup> | Typ² | Max <sup>1</sup> | Unit |

|--------------------|-------------------------------------|------------------------------------------------------|------|------------------|------|------------------|------|

| V <sub>IN</sub>    | Input Voltage Range                 | Scaled Input Voltage                                 | D    | 0                | 1.25 | 5                | V    |

| REG <sub>PID</sub> | Output Regulation                   | At Forward Converter output; $0 \le I_{LOAD} \le 2A$ | Q    | -5               |      | +5               | %    |

| LBW <sub>PID</sub> | Loop Bandwidth                      |                                                      | Q    |                  |      | 10               | KHz  |

| PM <sub>PID</sub>  | Phase Margin                        |                                                      | D    |                  | 70   |                  | Deg  |

| f <sub>Z1</sub>    | First Zero Frequency                | Filtered PID                                         | D    |                  | 1.7  |                  | KHz  |

| f <sub>Z2</sub>    | Second Zero Freq.                   | Differentiator<br>Response                           | D    |                  | 3.4  |                  | KHz  |

| f <sub>P1</sub>    | First Pole Frequency                | Integrator Response                                  | D    |                  | 3.4  |                  | KHz  |

| f <sub>P2</sub>    | Second Pole Freq.                   | Proportional Pole                                    | D    |                  | 56   |                  | KHz  |

| <b>f</b> ₽₩M       | PWM Switching Freq.                 |                                                      | D    |                  | 100  |                  | KHz  |

| DC <sub>MAX</sub>  | Max Clamped Duty<br>Cycle           |                                                      | Q    |                  | 65   |                  | %    |

| OCP                | Over Current<br>ProtectionThreshold |                                                      | т    |                  | 2.5  |                  | А    |

| T <sub>START</sub> | Startup Time                        | Due to soft start                                    | Q    |                  | 1    | 1.6              | ms   |

| I <sub>VDDA</sub>  | Current Drain                       |                                                      | D    |                  |      | 20               | μA   |

| I <sub>LKG</sub>   | Off-State Leakage<br>Current        |                                                      | D    |                  |      | 10               | nA   |

Notes: 1. Min and Max values are valid over Operating Conditions, unless otherwise stated.

2. Typ values are valid at typical Operating Conditions and typical process Parameters.

| Symbol          | Parameter             | Condition                                  | Test | Min <sup>1</sup> | Тур² | Max <sup>1</sup>            | Unit |

|-----------------|-----------------------|--------------------------------------------|------|------------------|------|-----------------------------|------|

| VIL             | Input Low Voltage     | $4.5 V \le V_{DDA} \le 5.5 V$              | D    | -0.3             |      | 0.8                         | V    |

| Vih             | Input High Voltage    | $4.5V \le V_{DDA} \le 5.5V$                | D    | 2.0              |      | V <sub>DDIO</sub> +<br>0.3V | V    |

| IILEAK          | Input Leakage Current | No Pull Up/Down                            |      | -10              |      | 10                          | μA   |

| I <sub>PD</sub> | Input with Pull Down  | At CTRLX, TSTMD<2:0><br>EN, TIMER1, TIMER0 |      | 3                | 15   | 40                          | μA   |

#### Table 14: CMOS Digital Inputs (TTL)

Notes: 1. Min and Max values are valid over Operating Conditions, unless otherwise stated. 2. Typ values are valid at typical Operating Conditions and typical process Parameters.

#### Table 15: CMOS Digital Outputs (TTL)

| Symbol          | Parameter           | Condition                     | Test | Min <sup>1</sup> | Тур² | Max <sup>1</sup> | Unit |

|-----------------|---------------------|-------------------------------|------|------------------|------|------------------|------|

| V <sub>OL</sub> | Output Low Voltage  | $4.5 V \le V_{DDA} \le 5.5 V$ | D    |                  |      | 0.4              | V    |

| V <sub>он</sub> | Output High Voltage | $4.5 V \le V_{DDA} \le 5.5 V$ | D    | 2.4              |      |                  | V    |

| I <sub>он</sub> | Output Current      | $4.5V \le V_{DDA} \le 5.5V$   |      |                  |      | 1                | mA   |

Notes: 1. Min and Max values are valid over Operating Conditions, unless otherwise stated. 2. Typ values are valid at typical Operating Conditions and typical process Parameters.

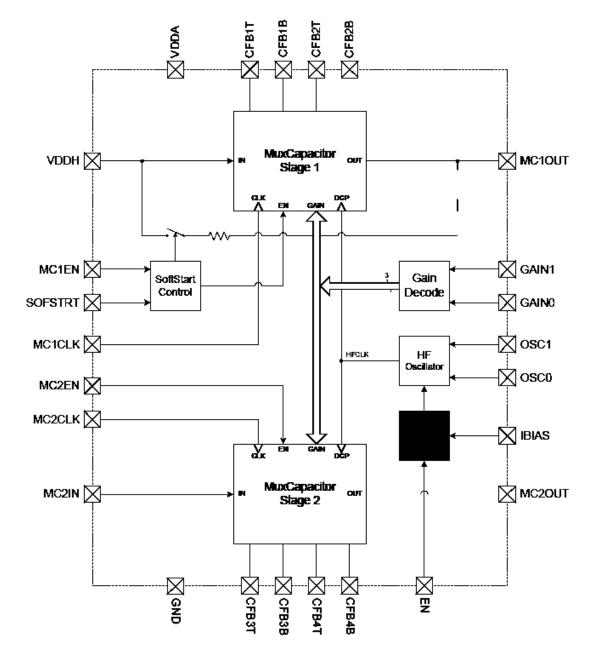

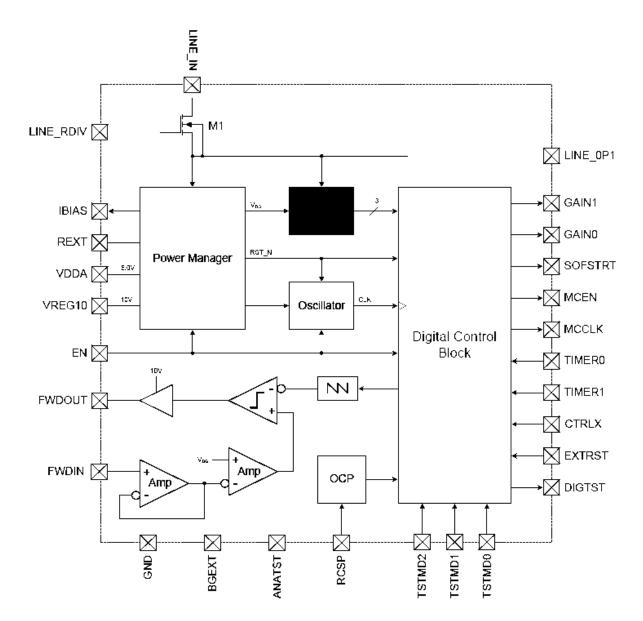

#### Figure 2: HS100 MuxCapacitor IC Block Diagram

#### Figure 3: HS100 Control IC Block Diagram

### 5 Functional Description

The Helix Semiconductors HS100 chip-set is comprised of two ICs: MuxCapacitor IC and Control IC. The HS100 chip-set reduces the rectified AC line voltages of 90V – 240V to 5.0VDC with an output current of up to 2.0A for AC line voltages 90- 120VAC or up to 1A for 220-240VAC.

#### 5.1 HS100 MuxCapacitor IC

The HS100 MuxCapacitor IC contains all of the high-voltage circuitry required for reducing the rectified AC Mains voltage to an optimal primary-side voltage for a forward converter isolation transformer. Startup and control of the MuxCapacitor IC is provided by the companion HS100 Control IC.

The block diagram of the HS100 MuxCapacitor IC illustrates the two MuxCapacitor voltage-divider stages and the required support circuitry. Each MuxCapacitor stage can be independently configured for either parallel or series connectivity as required by the application. For increased current capability, the two MuxCapacitor stages can be externally connected in parallel for 2X the current of a single MuxCapacitor stage.

For greater voltage division, the MuxCapacitors can be externally cascaded to provide a reduced voltage at the IC's output. For all cascaded (or series connected) applications the first MuxCapacitor stage must be connected to the highest input voltage at the VDDH pin. The MuxCapacitor output at MC10UT is then connected to the second MuxCapacitor input at MC2IN.

A Soft-Start current limiting switch is included to limit the inrush current from the VDDH input. Additional resistance in series with the switch limits the current to protect the MuxCapacitor power transfer switches until the external hold capacitor at MC1OUT is fully charged. The time period for the Soft-Start feature is controlled by the Control IC and output to the MuxCapacitor's SOFSTRT input.

An on-chip oscillator provides a 1.6MHz clock for the Dickson Charge Pump (DCP) voltage boosters. The voltage boosters provide the high side gate signals to the MuxCapacitor stages. The bias current for the Oscillator as well as the MuxCapacitor stages is provided by the IBIAS input.

#### 5.1.1 MuxCapacitor Voltage Divider

The HS100 MuxCapacitor IC voltage dividers reduce the DC voltage present at their input pins to a lower voltage at their respective MCxOUT pins. Each MuxCapacitor stage has a programmable gain of 1.0, 0.66 or 0.5 set by the GAIN1 and GAIN0 input pins. The truth table for the gain selection of the MuxCapacitor stages is shown in the table below.

| Inpu  | t Pin | MuxCapacitor Gain |         |  |  |

|-------|-------|-------------------|---------|--|--|

| GAIN1 | GAIN0 | Stage 1           | Stage 2 |  |  |

| 0     | 0     | 1                 | 1       |  |  |

| 0     | 1     | 0.66              | 0.66    |  |  |

| 1     | 0     | 0.5               | 0.5     |  |  |

| 1     | 1     | 0.66              | 0.5     |  |  |

#### Table 16: MuxCapacitor Gain Selection Truth Table

Each MuxCapacitor stage can deliver up to 50mA of current. The output voltage is dependent on the gain setting and the input voltage. Two external fly-back capacitors and a hold capacitor are required per MuxCapacitor stage. These capacitors are connected to the CFBxT, CFBxB, and MCxOUT pins, respectively. The MuxCapacitor stages are clocked at a rate of up to 1KHz from the MCxCLK input clock pin. The duty cycle of the clock is 50%.

#### 5.1.2 Dickson Charge Pumps

The Dickson Charge Pumps (DCP's) are used to provide a boosted voltage for the gates of the NMOS high-voltage switches. The MuxCapacitor has multiple high side switches and each switch has a DCP that is clocked at 1.6 MHz. The DCPs generate a voltage that is 15V greater than the voltage at the MuxCapacitor's input pin. The DCP's clock is provided by the High-Frequency Oscillator.

#### 5.1.3 Level Shifters

Each NMOS high-voltage switch has a corresponding level shifter to translate the drive signal from the low-voltage domain to the boosted voltage provided by the DCP's. Each high-voltage switch has an optimally sized level shifter based on its gate drive characteristics.

#### 5.1.4 Soft-Start Current Limiter

A Soft-Start current limiting switch is provided for the first MuxCapacitor stage to limit in-rush current at startup. The switch and a series connected resistor are placed in parallel with the primary power

switches from the input to the output of the MuxCapacitor stage. The current is limited by the resistor when the switch is enabled.

The Soft-Start sequence is initiated and controlled by a programmable timer located in the HS100 Control IC. During the SOFTST timer period all MuxCapacitor power transfer switches are disabled to eliminate any low-resistance paths from input to output. Once the timer completes the cycle, all switches are then enabled for normal operation. The current limiting switch is enable by setting the SOFTST pin high. The MuxCapacitor is enabled by setting the MC1EN pin high. Therefore, during soft start, SOFTST = 1 and MC1EN = 0. For normal operation, SOFTST = 0 and MC1EN = 1.

#### 5.1.5 3.2MHz Oscillator

The 3.2MHz Oscillator provides the high-frequency clock for the HS100 MuxCapacitor IC. It contains a divide-by-two to produce a 1.6MHz, 50% duty cycle clock for the Dickson Charge Pumps for each MuxCapacitor stage. The frequency of the oscillator can be programmed with the OSC1 and OSC0 pins according to the following table.

| Inpu | t Pin | Oscillator |

|------|-------|------------|

| OSC1 | OSC0  | Frequency  |

| 0    | 0     | 1.6MHz     |

| 0    | 1     | 0.8MHz     |

| 1    | 0     | 0.4MHz     |

| 1    | 1     | Disabled   |

#### **Table 17: Oscillator Frequency Control**

#### 5.2 HS100 Control IC

The HS100 Control IC provides all the low-voltage bias and support circuitry required for startup and control of the HS100 MuxCapacitor IC and the external Forward Converter.

The rectified AC-Mains voltage is input at the LINE\_IN pin to provide power to the Control IC. An onchip source follower M1 reduces the voltage for internal Low Drop-Out (LDO) regulators. An external resistor divider at the LINE\_RDIV pin provides the gate bias for M1 such that the voltage at LINE\_OP1 (M1 drain) is 1/10 of the incoming LINE\_IN voltage. The LINE\_OP1 voltage is used to supply all of the internal circuits on the Control IC.

The LINE\_OP1 voltage is also used to sense the incoming AC-Mains voltage and is input to the Country Selector. The Country Selector determines the proper gain setting for the MuxCapacitor IC by setting the GAIN0 and GAIN1 outputs of the Digital Control Block as a function of the region of operation, i.e. Japan/US or Universal.

The Power Manager provides all the reference voltages and currents for the Control IC. The following circuits reside within the Power Manager: Bandgap Voltage Reference, 5.0V Linear Voltage Regulator (LVR) and Power-on-Reset (POR). These cells are always powered on when the LINE\_IN voltage is applied and cannot be disabled. The Power Manager also contains a Voltage-to-Current Converter (VTOI) which sources current for use by all on-chip analog circuits. The VTOI reference is a precision external resistor connected to the REXT pin. In addition, a 1µA current is replicated and output at the IBIAS pin for use by the MuxCapacitor IC. The EN pin is used to disable the VTOI and Current Manifold for reduced power consumption during idle mode of operation.

The 5.0V LVR supplies the voltage for the Digital I/O on the Control IC and also supplies the VDDA supply voltage for the MuxCapacitor IC. A 10V LVR is also provided at the VREG10 pin to supply the voltage for the Forward Converter output driver connected to the FWDOUT pin.

The Control IC also provides the circuitry required to control an external Forward Converter using an Opto-Isolator feedback circuit. The analog Opto-Isolator input singal at the FWDIN pin is converted to a Pulse-Width-Modulated (PWM) signal to control an external MOSFET connected at the FWDOUT pin. Pulse-Width-Modulation is performed at a rate of 100KHz with a clock provided by the on-chip RC Oscillator.

The Digital Control Block provides logic for the configuration of the MuxCapacitor IC and control of the Forward Controller. The MCEN and MCCLK outputs provide the enable and clock for the MuxCapacitor IC. All clocks used on the Control IC are derived from the on-chip 200KHz Oscillator. This clock is divided down to 100KHz for the Forward Controller and to 1KHz for the MCCLK output. The Digital Control Block also contains a programmable timer for the Soft-Start control of the

MuxCapacitor IC via the SOFSTRT pin. Testibility logic is also provided for the Control IC and is controlled as a function of the TESTMD<2:0> input pins and the EXTRST pin.

The Control IC can be disabled using the EN input pin. When EN=0, the Control IC will be disabled and all analog and digital circuits are turned off.

#### **5.2.1 Line-Side Bandgap Voltage and Current Reference Generator**

The Control IC contains an ultra-low power Bandgap Reference Voltage and Current generator which is powered from LINE\_OP1. A temperature-compensated output voltage of 1.22V is provided for use as a reference by subsequent circuit blocks. The bandgap cell is self-starting at the application of the LINE\_IN voltage and is always powered on and cannot be disabled.

An optional external shunt Bandgap can be used in place of the internal Bandgap Voltage Reference. The external Bandgap device is connected to the BGEXT pin and is selected when the CTRLX pin is asserted 'high'. The required external Bandgap voltage is 1.25V.

#### 5.2.2 5.0V Linear Voltage Regulator

The 5.0V Linear Voltage Regulator (LVR) is used to supply the voltage for the analog and digital circuits, and the I/O padring of the Control IC. The output of the Regulator is available at the VDDA pin to power the MuxCapacitor IC. An external  $10\mu$ F caoacitor must be connected between VDDA and ground for noise reduction.

The 5.0V LVR is always powered on at the application of the LINE\_IN voltage and cannot be disabled.

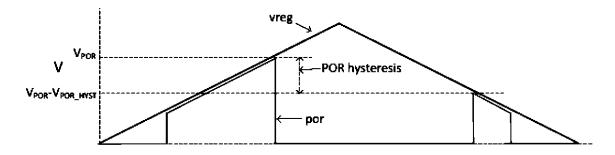

#### 5.2.3 Power-on-Reset

The Power-on-Reset (POR) circuit monitors the internal VDDA supply voltage. For voltages at the VDDA pin less than the VPOR threshold voltage, the POR output will be asserted 'low' indicating a reset condition. For voltages at the VDDA pin greater than the VPOR threshold voltage, the POR output will be de-asserted 'high' for normal operation. Hysteresis is provided such that a reduction in the threshold voltage occurs once the VPOR threshold is exceeded. The reduced threshold with hysteresis now becomes VPOR - VHYS.

An illustration of the operation of the power-on-reset block for a voltage ramp at the VDDA pin is shown below. The POR circuit is always powered on at the application of the LINE\_IN voltage and cannot be disabled.

### Figure 4: POR Threshold Voltages

#### 5.2.4 VTOI and Current Manifold

The Voltage-to-Current Converter (VTOI) produces a current referenced from an external precision resistor connected to the REXT pin. Using the Bandgap reference voltage, the VTOI generates a 0.5V bias at the REXT pin. With the connection of a 499K $\Omega$ , 1% resistor from REXT to ground, a precision 1µA current is generated. The Current Manifold uses this precision current to supply the bias currents to the analog circuits in the Control IC. A 1µA reference current is also output at the IBIAS pin for use by the MuxCapacitor IC.

#### 5.2.5 Oscillator

The ultra-low power 200 KHz RC Oscillator produces the low-frequency clocks for the Control IC. The output of the oscillator is divided down to 100KHz for the Digital Control Block which provides clocks to the MuxCapacitor IC and the Forward PID Controller.

#### 5.2.6 10V Linear Voltage Regulator

The 10V LVR provides the supply voltage for the Forward Converter output driver at the FWDOUT pin. The output of the 10V LVR is available at the VREG10 pin. An external  $10\mu$ F caoacitor must be connected between VREG10 and ground for noise reduction.

### 5.2.7 Forward PID Controller

The Forward PID Controller controls the external MOSFET of the Forward Converter using an optoisolator feedback circuit. The feedback voltage signal is input at the FWDIN pin and is compared to the Bandgap voltage to generate an error voltage for the loop. The Error Amplifier creates a 3rd order compensation network with on-chip passive components. The resulting transfer function of the PID Feedback Loop is comprised of 2 poles and 2 zeros to ensure that the regulator output is stable for the full range of load conditions.

The two zeroes provide 180 degree of phase boost in order to negate the 180 degree of phase loss due to the output LC filter. Both zeroes are placed at 50% of the LC filter pole frequency. The two poles are located at the switching frequency of the converter (100KHz). The Forward PID Feedback Loop uses Pulse-Width Modulation (PWM) to control the amount of time the external MOSFET switch is turned 'on' to supply current to the load. This is achieved with a comparator which receives the output of the Error Amplifier and compares it to the sawtooth waveform output of the Sawtooth Generator. The 100 KHz clock provided by the Digital Control Block is used by the Sawtooth Generator to develop the sawtooth input to the Comparator.

#### 5.2.8 Country Selector

The Country Selector uses the scaled LINE\_IN voltage at LINE\_OP1 to determine the appropriate gain (or divider ratio) for the MuxCapacitor stages of the MuxCapacitor IC. The scaled LINE\_IN voltage is compared to the Bandgap reference voltage to output one of the possible gain settings as a function of the AC Mains voltage. The outputs of the Country Selector are input to the Digital Control Block to decode the appropriate gain setting required by the MuxCapacitor IC.

#### **5.2.9 Over-Current Protection**

Overcurrent protection for the Forward Converter is achieved by sensing the current flowing through the external switching MOSFET and the primary winding of the transformer. The voltage developed across the external current sense resistor is placed in series with the MOSFET and transformer is applied to the pin RCSP. This RCSP voltage is compared to a reference voltage. When an over-current condition is detected the Forward PID Controller is disabled and the DIGTST output pin will be asserted 'high'. The Forward PID Controller will remain disabled until the TSTMD2 input is momentarily asserted 'high'. Then the Forward Converter operation will be restored.

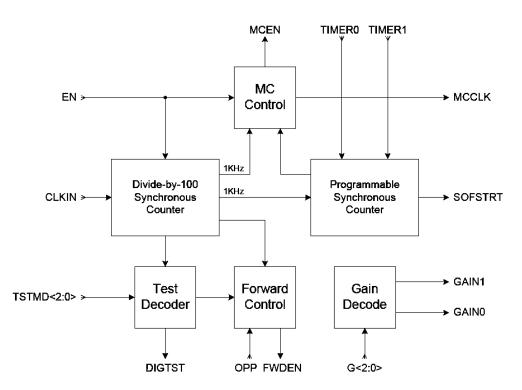

### 5.3 Digital Control Block

The Digital Control Block provides the logic control and configuration of the MuxCapacitor IC as well as control of the Forward PID Controller. The block diagram of the Digital Control Block is shown below.

Figure 5: Digital Control Block Diagram

All clocks used in the Control IC are derived from the on-chip Oscillator which is divided down by a 5bit synchronous counter to create the 1KHz for the MCCLK output. The 1KHz output of the counter is also used for the programmable Soft-Start timer for the SOFSTRT pin. The Soft-Start timer is programmable to one of four possible timeout values using the TIMERO and TIMER1 input pins as shown below.

| TIMER1 | TIMER0 | SOFSTRT<br>Timeout (mS) |

|--------|--------|-------------------------|

| 0      | 0      | 10                      |

| 0      | 1      | 30                      |

| 1      | 0      | 20                      |

| 1      | 1      | 40                      |

#### **Table 18: Soft-Start Timer Program Settings**

The Gain Decode block receives the Country Selector outputs and creates the GAIN0 and GAIN1 outputs to control the MuxCapacitor IC gain setting

The Forward Control block provides the enable for the Forward PID Controller and also disables the block when an over-current detection is detected at the *OPP* input of the RCSP pin. Following the over-current event detection, the *OPP* signal is reset by the assertion of the TSTMD<2> input pin.

Logic is also provided for testing the Control IC as a function of the TESTMD<2:0> input pins and the EXTRST pin. When the EXTRST pin is asserted 'high' all of the digital logic is reset overriding the internal Power-on-Reset. The three TSTMD inputs provide access to internal analog and digital signals through the use of digital and analog multiplexers. Internal digital signals can be multiplexed to the DIGTST output and internal analog signals can be multiplexed to the ANATST pin. The truth table for the digital test mode inputs is shown below.

| Test Select Input Pins |        |        | Function                            |  |  |

|------------------------|--------|--------|-------------------------------------|--|--|

| TSTMD2                 | TSTMD1 | TSTMD0 | Function                            |  |  |

| 0                      | 0      | 0      | DIGTST = Over-Current Detect Output |  |  |

| 0                      | 0      | 1      | DIGTST = Forward Clamp Comparator   |  |  |

| 0                      | 1      | 0      | DIGTST = Forward Softstart OK       |  |  |

| 0                      | 1      | 1      | DIGTST = 100KHz Oscillator Output   |  |  |

| 1                      | 0      | 0      | Reset Over-Current Detection        |  |  |

| 1                      | 0      | 1      | Disable Forward PID Controller      |  |  |

| 1                      | 1      | 0      | ANATST = Bandgap Voltage            |  |  |

| 1                      | 1      | 1      | Logic Test Mode                     |  |  |

#### Table 19: Test Select Truth Table

When TSTMD<2:0> = 3'b111, the Logic Test Mode is enabled. This allows an external clock to be input at the CTRLX pin bypassing the on-chip oscillator. A higher-speed clock can be used to test the digital logic reducing the test time.

The digital inputs of the Control IC are configured as a NAND-Tree allowing the inputs to be tested at wafer probe or package test. When the EXTRST pin is asserted 'high' the NAND-Tree is enabled with the output muxed to the MCEN output pin. The test begins with all inputs asserted 'high' as shown below. They are sequentially taken 'low' in the order shown in the table.

| CTRLX | TSTMD2 | TSTMD1 | TSTMD0 | EN | TIMER1 | TIMER0 | MCEN |

|-------|--------|--------|--------|----|--------|--------|------|

| 1     | 1      | 1      | 1      | 1  | 1      | 1      | 1    |

| 0     | 1      | 1      | 1      | 1  | 1      | 1      | 0    |

| 1     | 0      | 1      | 1      | 1  | 1      | 1      | 0    |

| 1     | 1      | 0      | 1      | 1  | 1      | 1      | 0    |

| 1     | 1      | 1      | 0      | 1  | 1      | 1      | 0    |

| 1     | 1      | 1      | 1      | 0  | 1      | 1      | 0    |

| 1     | 1      | 1      | 1      | 1  | 0      | 1      | 0    |

| 1     | 1      | 1      | 1      | 1  | 1      | 0      | 0    |

#### Table 20: NAND-Tree Test Sequence

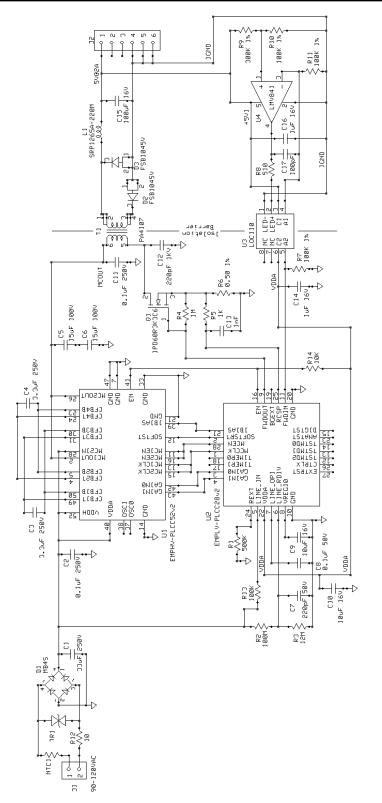

### 6 Reference System Application

The following system diagram provides a 10W application schematic for a 5.0V output. The HS100 chip-set is combined with a Forward Converter delivering the specified efficiency for a load of 50mA to 2.0A. In this configuration the MuxCapacitor stages of the MuxCapacitor IC are connected in parallel to deliver 100mA at the input to the transformer primary.

Other configurations are possible including World-wide applications.

The electrical characteristics of the HS100 Reference System are summarized.

| Symbol               | Parameter              | Condition                    | Min  | Тур | Мах  | Unit     |  |

|----------------------|------------------------|------------------------------|------|-----|------|----------|--|

| V <sub>AC</sub>      | AC Input Voltage       | US-only operation            | 108  | 120 | 132  | VAC      |  |

|                      |                        | World-wide operation         | 90   |     | 240  |          |  |

| V <sub>LINE_IN</sub> | DC Line Voltage        | US-only operation            | 152  | 170 | 187  | VDC      |  |

|                      |                        | World-wide operation         | 127  |     | 340  |          |  |

| Fin                  | Input Frequency        |                              | 47   |     | 63   | Hz       |  |

| V <sub>PRIM</sub>    | Primary Voltage        |                              |      | 110 |      | V        |  |

| Q <sub>ir</sub>      | In-Rush charge         |                              |      |     | TBD  | Coulombs |  |

| Vo                   | Output Voltage         | Average voltage              | 4.75 | 5.0 | 5.25 | Vdc      |  |

| l <sub>o</sub>       | Output Current         |                              | 0    |     | 2.0  | A        |  |

| Pout                 | Output Power           |                              |      |     | 10   | W        |  |

| V <sub>oa</sub>      | Output Accuracy        |                              | -5.0 |     | +5.0 | %        |  |

| VR                   | Voltage Regulation     | $50mA \le I_{LOAD} \le 2.0A$ |      |     | TBD  | %        |  |

| V <sub>RIPPLE</sub>  | Output Voltage Ripple  |                              | -2   |     | +2   | %        |  |

| V <sub>td</sub>      | Voltage Temp drift     |                              |      |     | TBD  | % / °C   |  |

| EF <sub>fl</sub>     | Efficiency, Full Load  | Pout/Pin                     | 95   |     |      | %        |  |

| EF                   | Efficiency, Light Load | Pout/Pin                     | 92   |     |      | %        |  |

| Pni                  | No Load Power Output   |                              |      |     | 10   | m₩       |  |

#### Table 21: HS100 System Characteristics

Figure 6: HS100 Japan/USA Application Schematic

Figure 7: HS100 Universal Application Schematic

### 7 Package Drawings

The packages for the HS100 MuxCapacitor and Control IC's are shown in the following drawings.

#### 7.1 MuxCapacitor IC